# **MEMS** Packaging

#### ESS4810 Lecture Fall 2010

### Contents

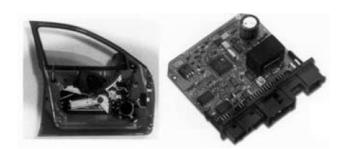

- Microsystems Packaging

- Electronics Packaging

- Bonding

- MEMS Packaging

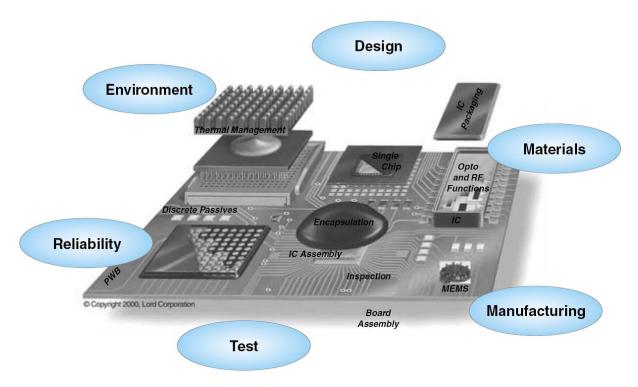

# **Microsystems Packaging**

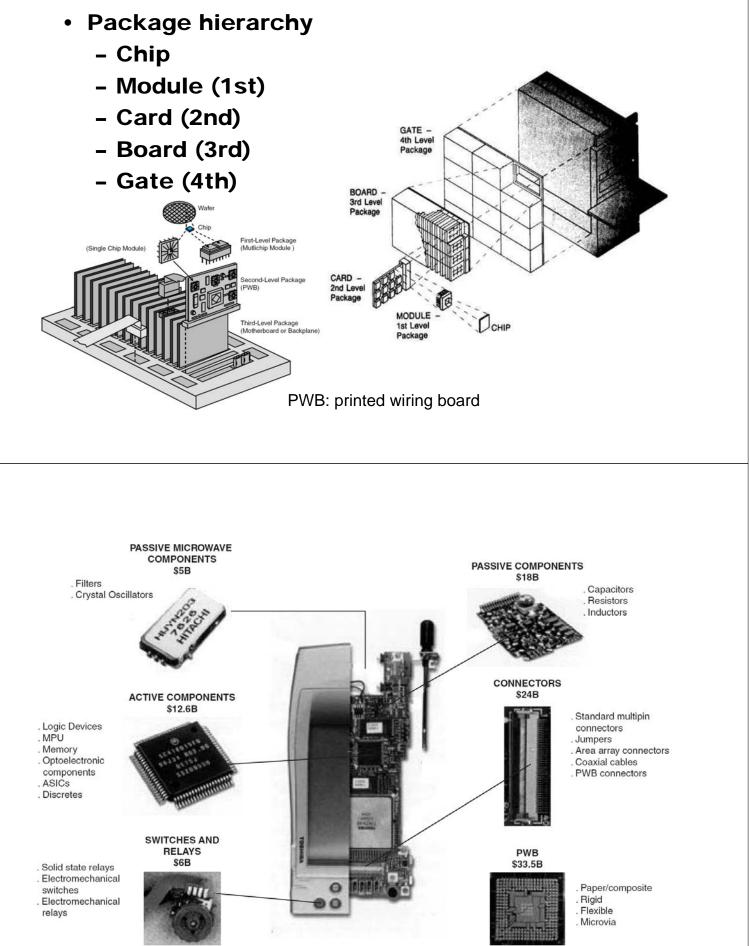

- A \$125 billion worldwide market, employing more than a million people

- Miniaturized and integrated systems

- Microelectronics, Photonics, MEMS and RF Devices

- Systems Engineering

- Systems Packaging

- Packaging is defined as the bridge that interconnects the ICs and other components into a system to form electronic products

# **Microsystems Packaging**

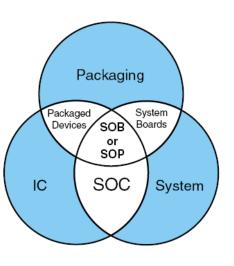

# Integration

- System-on-Board (SOB): a number of packaged ICs and other components assembled onto a system-level board

- System-on-Chip (SOC)

- System-on-Package (SOP), or System-in-Package (SIP) is analogous to SOC, in that it is a single component, multifunction, multi-chip package providing all the needed system-level functions

- Both SOC and SOP are expected to be the wave of the future.

## **IC and MEMS Packaging**

- IC Packaging

- The approximate IC fabrication cost, excluding design cost, is about \$4/cm<sup>2</sup> at mature production levels

- Well-developed (dicing, wire bonding, ...)

- 30% to 95% of the whole manufacturing cost

- MEMS Packaging

- Specially designed packaging processes

- Difficult due to moving structures, chemicals ...

- The most expensive process in microfabrication

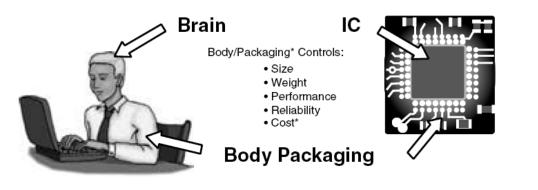

# **Electronics Packaging**

- Electronics have to be packaged

- Functions:

- Protecting, powering, and cooling

- Electrical and mechanical connection/ interface

- Challenge:

- Providing all crucial functions required without limiting the performance

Human

**Electronic System**

(a) Inside a Computer

(b) Inside a Celluar Phone

(c) Inside an Automobile

# **Electronics Packaging**

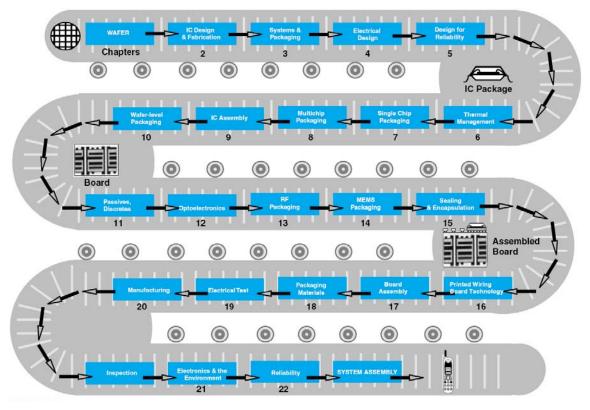

#### **Critical Microsystem Packaging Technologies** from Wafer to System-Level Board

#### **IC Packaging**

|                            |   | Through Hole Packages |                                             |   | Surface Mount Packages |                                                                  |

|----------------------------|---|-----------------------|---------------------------------------------|---|------------------------|------------------------------------------------------------------|

| Wafer & IC                 | a | and and and           | DIP (Dual In-line<br>Package)               | g |                        | SO or SOP<br>(Small Out-<br>Package)                             |

|                            | b | 000000                | SH-Dip<br>(Shrink DIP)                      | h |                        | CFP<br>(Quad Flat<br>Package)                                    |

| WB FC TAB                  | с | 0000000               | SK-DIP, SL-DIP<br>(Skinny DIP,<br>Slim DIP) | i |                        | LCC<br>(Leadless<br>Chip Carrier)                                |

| Discrete L,C,R Packaged IC | d | O O                   | SIP<br>(Single In-<br>Package)              | j |                        | PLCC, SOJ<br>(Plastic Leader<br>Chip Carrier with<br>Butt Leads) |

| BOARD ASSEMBLY             |   | TPYTTI                |                                             | k | 0000000                | BGA<br>(Ball Grid Array)                                         |

| Battery                    | e | TPTTTTTT              | ZIP<br>(Zig-zag In-line<br>Package)         | I |                        | TAB<br>(Tape Automated<br>Bonding)                               |

| SYSTEM ASSEMBLY            | f |                       | PGA (Pin Grid Array)<br>or Column Package   | m |                        | CSP<br>(Chip Scale<br>Package)                                   |

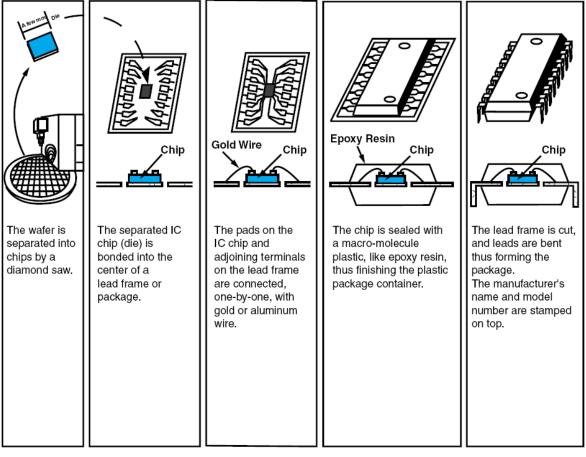

FIGURE 2.22 An example of dual in-line IC packaging with wirebonding.

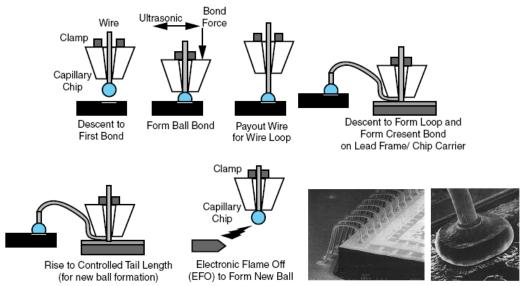

## WireBonding

A chip-to-package interconnection technique where a fine metal wire is attached between each of the I/O pads on the chip and its associated package pin, one at a time

#### Wafer Level Packaging

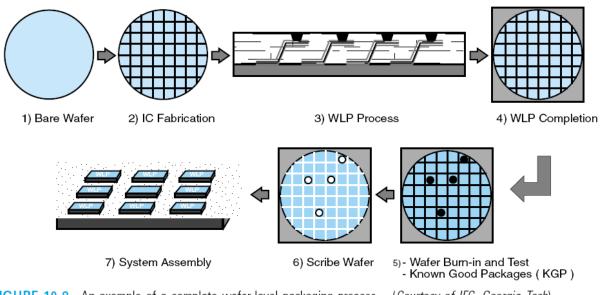

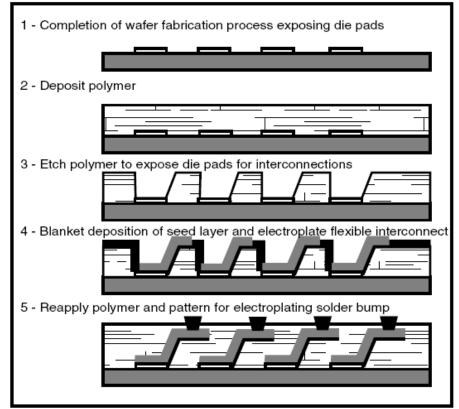

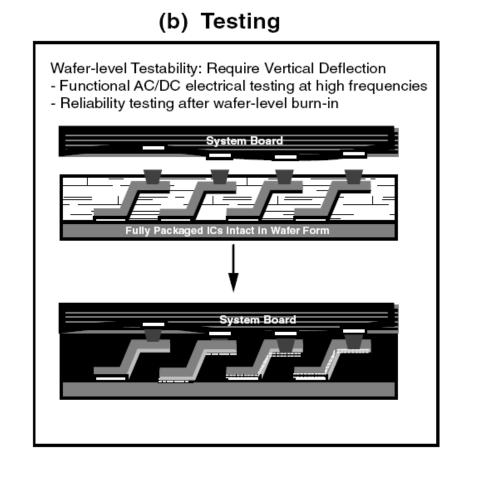

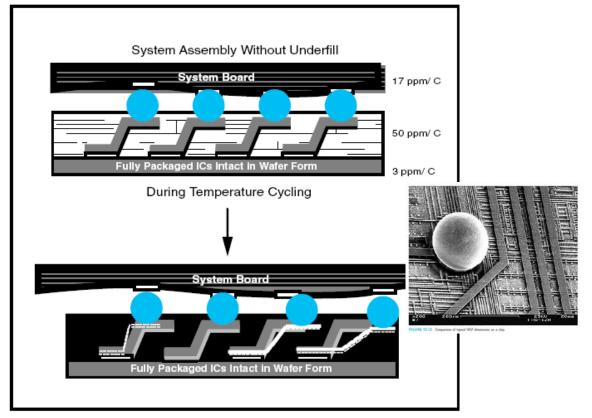

FIGURE 10.8 An example of a complete wafer-level packaging process. (Courtesy of IFC, Georgia Tech)

#### (c) System Assembly

# Bonding

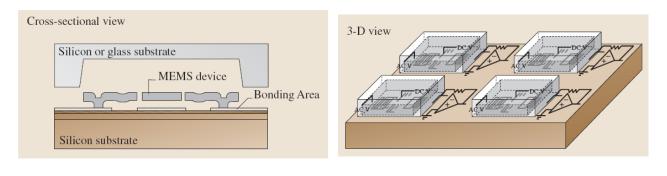

- Permanently seal solid-state materials with smooth and flat surfaces, most often by chemical reactions

- Allow the fabrication of multi-layer, sandwiched, micromechanical structures, in which each layer can contain threedimensional structures

- Allow the multi-chip production of microsystems with many micromechanical structures and/or microelectronic structures bonded to the single silicon or glass substrate platform

- Very good techniques for packaging of microsystems

### **Basic Requirements**

- Surface cleanliness

- Particles trapped between wafers can lead to the formation of voids and failure of the bond

- Minimal process-induced stress

- Thermal mismatch

- Stable and strong

- Strain relief

# Bonding

- Carried out in the range of high (>700°C), medium (200~500°C) or low temperatures (20~200°C)

- Fusion bonding

- Anodic (electrostatic) bonding

- Eutectic bonding

- Adhesive bonding

# **Fusion Bonding**

- Joining silicon to silicon

- Placing the surfaces in close contact, inserting them in an oxidizing ambient at temperatures > 800°C (not IC compatible), and then annealing

- Quality

- Depending critically on temperature (> 1000°C) and roughness (< 4 nm)</li>

- Strength up to 20 MPa

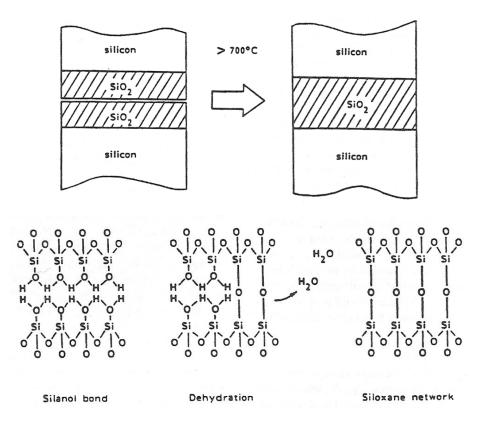

## **Fusion Bonding**

- Chemical reaction between OH-groups (native or grown oxide)

- Wafers must undergo hydration to create hydrophilic top layer consisting O-H bonds

- Bonding systems

- Si + Oxidized Si wafer

- two Oxidized Si wafer

- two bare Si wafers

- Si + Si with a thin layer (< 200 nm) nitride

### **Bonding Mechanism**

## **Fusion Bonding**

- Bond strength after various annealing temperatures

- < 300°C:

- bond strength remains the same as spontaneous bond

- 300°C 800°C:

- voids can be formed (possibly due to water molecules)

- 800°C:

- bond strength increases to about the fracture strength of single crystal silicon of 10 to 20 MPa (at 1000°C)

- Low temperature bonding processes have been reported

- < 150°C for 10 to 400 hrs</li>

- Energetic particle bombardment (argon at 1.5 keV)

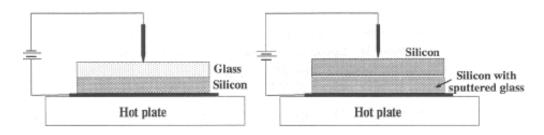

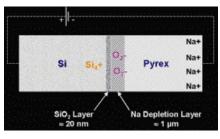

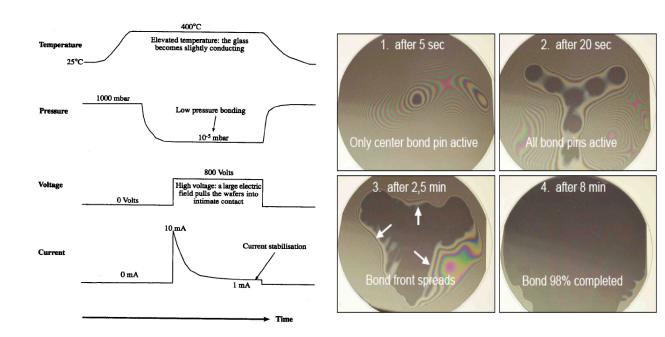

## **Anodic Bonding**

- Joining glass to silicon

- Field-assisted thermal bonding

- 180°C < process temperature < 500°C

- 200 V < operating voltage < 1000 V

- Depending on thickness and temperature

- 5 min < process time < 10 min

#### **Bonding Mechanism**

- Electrostatic attraction to facilitate bonding

- Extremely mobile positive ions, mainly sodium, in the glass drift towards the negative electrode leaving a negative charge on the glass side of the silicon-glass interface

- A high electric field is generated between this fixed negative charge and positive charge in the silicon, thus pulling the glass and silicon together and facilitating the chemical bond

- Covalent bonds are formed

# **Bonding Process**

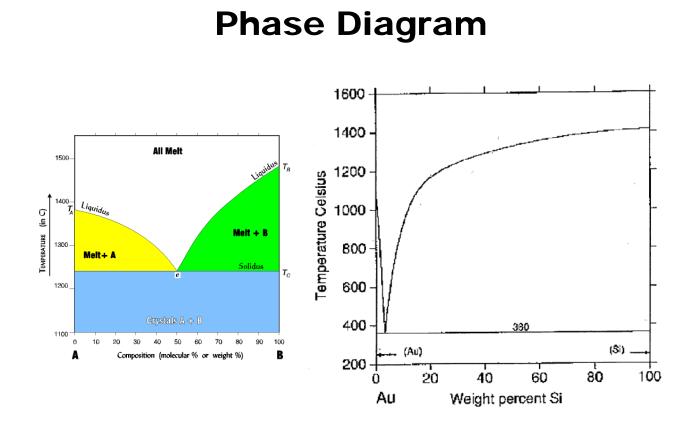

#### **Eutectic Bonding**

- Utilizing the eutectic properties of two materials combined, the combination having a lower melting point than each of the individual ones

- A typical composition is 97.1% Au and 2.85% Si by weight, which can be bonded at 386°C

- Placing the gold in contact with the silicon and heating, causing the gold atoms to diffuse into the silicon

- When the eutectic composition is reached, a liquid layer is formed at the interface and the eutectic alloy grows until the gold is exhausted

- The alloy can then be cooled slowly, causing it to solidify and hence forming the bond

#### **Eutectic Bonding**

- The gold can be deposited on one of the silicon surfaces by evaporation or sputtering and functions as the intermediate layer for bonding

- The joints formed are hermetic with strength up to 148 MPa

- A drawback with this process is that the mismatch in thermal expansion coefficients results in high residual stresses within the alloy

- In addition, these stresses change with time due to creep

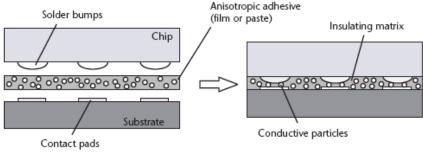

## **Adhesive Bonding**

- Commercially available adhesives

- Photo-patternable polymers

- Generally can be achieved at temperatures under 150°C and are relatively soft, providing some degree of stress relief for the wafers

- They are, unsuitable for hermetic seals, can degrade over long periods of time, and can possess poor thermal stability

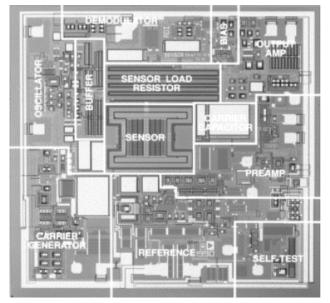

## **MEMS Packaging Issues**

- Accelerometer

- Surfacemicromachined accelerometers by Analog Devices, Inc.

- Free standing microstructures

- Hermetic sealing

- Temperature sensitive microelectronics

ADXL50 by Analog Devices, Inc.

### **MEMS Packaging Issues**

- Pressure sensor

- Bulk micromachined pressure sensor by Motorola Inc.

- Exposure to external pressure source

- Housing for harsh environment

- Interface coating

Motorola's MEMS-based pressure sensor

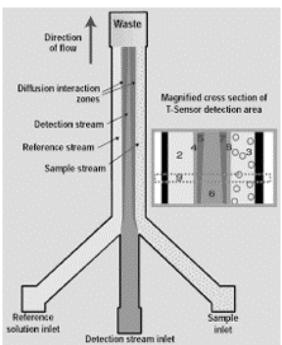

#### **MEMS Packaging Issues**

- Microfluidics

Diffusion-based

- sensor by Micronics

- Micro-to-macro interconnector

- Good sealing

- Temperature sensitive materials

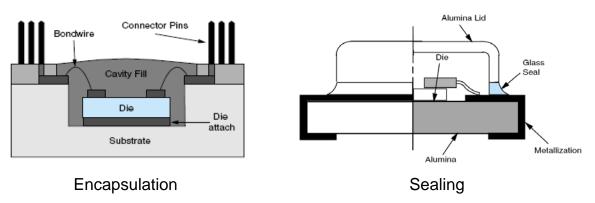

#### **Encapsulation and Sealing**

- Encapsulation provides an economical way to protect device packages by isolating the active devices from environmental pollutants, and at the same time offering mechanical protection by structural coupling of the device to the constituent packaging materials into a robust package

- This type of organic coating is a very inexpensive way of protecting devices, but their protection is not permanent, typically controlled by permeation properties of the polymeric resins used

- The inorganic sealing, however, is permanent, by being hermetic, but the cost of this process is high

# **Encapsulation and Sealing**

Performance is determined by its dimensional stability, its resistance to thermal excursions, its permeation providing isolation of environmental pollutants and its thermal dissipation providing dissipation of the heat generated by the packaged device

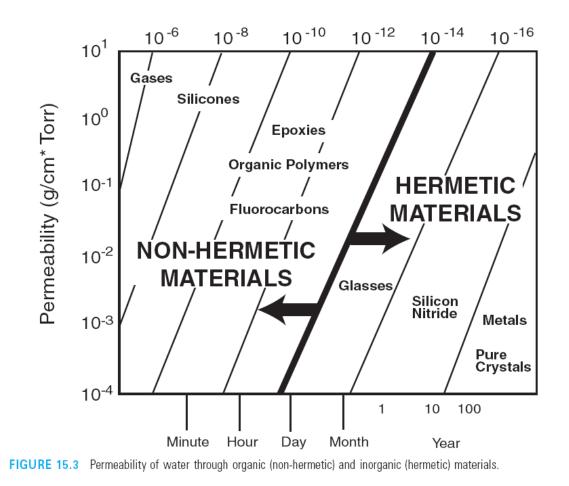

### **Hermetic Seal**

- MIL-STD-883

- A seal that will indefinitely prevent the entry of moisture and other contaminants into the cavity

- In practice such seals are non existent

- Smaller gas molecules will enter the cavity over time by diffusion or permeation and reach equilibrium

#### **Hermetic Packaging**

- The permeability to moisture of glasses, ceramics and metals is orders of magnitude lower than plastic materials

- Metal package

- harshest conditions, 80% of all metal packages are welded, with the remaining being soldered

- Ceramic package

- Solder glass seal by high-lead-content vitreous or de-vitrifying glasses at 400°C

- Hard glass seal by high-melting borosilicate glass at 1100°C

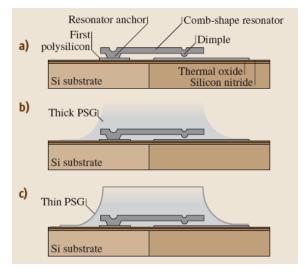

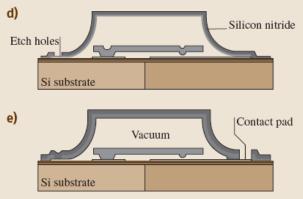

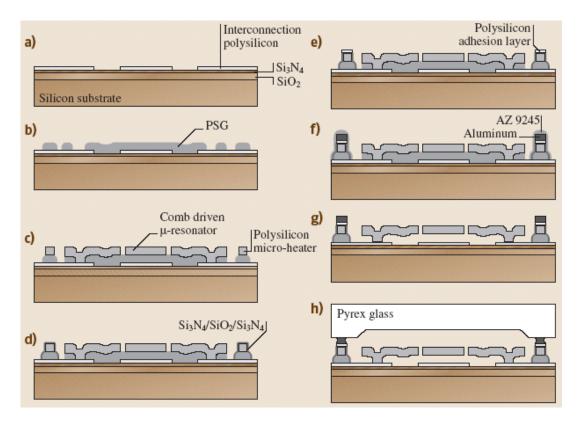

## **Encapsulation Processes**

- LPCVD process

- (a) standard surface micromachining process

- (b) additional thick PSG deposition to define encapsulation regions

- (c) additional thin PSG deposition to define etch channels

#### **Encapsulation Processes**

- LPCVD process

- (d) nitride shell deposition; etch hole definition

- (e) removal of all sacrificial PSG inside the shell; supercritical CO<sub>2</sub> drying; global LPCVD sealing

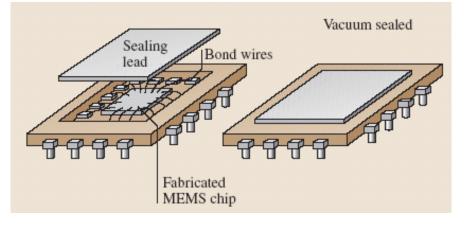

# **Packaging Process**

- Electrical interconnects

- Die attachment

- Sealing

# **Electrical Interconnects**

- Wire bonding

- Tape automated bonding

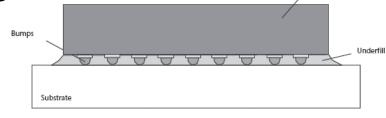

- Flip chip

- Placing the die face-down (flipped) onto the package or circuit board

- The electrical connection is made by conductive bumps formed on the die bond pads

#### Process

#### Three stages

- (1) Bumping the die or wafer

- (2) Attaching the bumped die to the board or substrate

- (3) Underfilling the remaining space under the die with an electrically insulating material

## **Advantages**

- Reduced package size

- High-speed electrical performance due to the shortened path length

- Greater flexibility of contact pad location

- Mechanically rugged

- Lowest cost interconnection method for high-volume production

#### **Die attachment**

- Adhesive die attach

- Soldering die attach

- Eutectic bonding

- Glass die attach

| Relative Ments of Die Attachment Methous                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advantages                                              | Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Low cost                                                | Outgases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Easily automated                                        | Contamination/bleed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Low curing temperatures                                 | Susceptible to voids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Reduced die stress                                      | Inferior thermal/electrical conductivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Special plated surfaces not required<br>Rework possible | Can require careful storage (e.g., –40°C)<br>and mixing before use                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                         | Not suited to harsh environments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Good electrical/thermal conductivity                    | Requires wettable metallized surfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Good absorption of stresses arising from                | on the die and substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| of thermal expansion coefficients<br>mismatches         | Usually requires processing temperatures<br>greater than 200°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| "Clean"                                                 | Needs flux or an inert gas atmosphere                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Rework possible                                         | Porosous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                         | Poor thermal fatigue resistance of some<br>alloys                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Good thermal conductivity                               | Poor absorption of stresses arising from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Electrically conducting                                 | of thermal expansion coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Good fatigue/creep resistance                           | mismatches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Low contamination                                       | High processing temperatures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| "High" process/operating temperature                    | Die back metallization may be required                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| capability                                              | If bare die are used, a scrubbing action is<br>required to break down surface oxide                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                         | Rework difficult                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Low void content                                        | High processing temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Good thermal/electrical conductivity                    | Glass requires an oxygen atmosphere,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Limited stress relaxation                               | which can lead to oxidation of other                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Low contamination                                       | plated systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| High process/operating temperature<br>resistance        | Not commonly used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                         | AdvantagesLow costEasily automatedLow curing temperaturesReduced die stressSpecial plated surfaces not requiredRework possibleGood electrical/thermal conductivityGood absorption of stresses arising fromof thermal expansion coefficientsmismatches"Clean"Rework possibleGood thermal conductivityElectrically conductingGood fatigue/creep resistanceLow contamination"High" process/operating temperaturecapabilityLow void contentGood thermal/electrical conductivityLimited stress relaxationLow contaminationHigh process/operating temperature |

#### Table 4.2 Relative Merits of Die Attachment Methods

#### **Packaging of Mechanical Sensors**

- Protect the sensor from external influences and environmental effects

- Protect the environment from the presence of the sensor

- Provide a controlled electrical, thermal, mechanical, and/or optical interface between the sensor, its associated components, and its environment

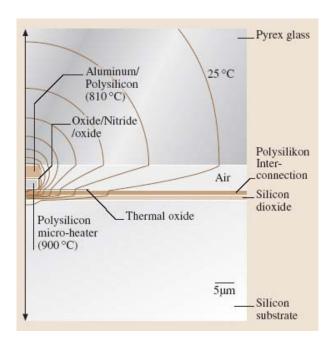

#### **Localized Bonding**

- Achieve high temperature for bonding while maintaining low temperature globally at the wafer level

- The heating region can be confined locally as long as the bottom Si substrate is constrained to the ambient temperature

# **Bonding Process**

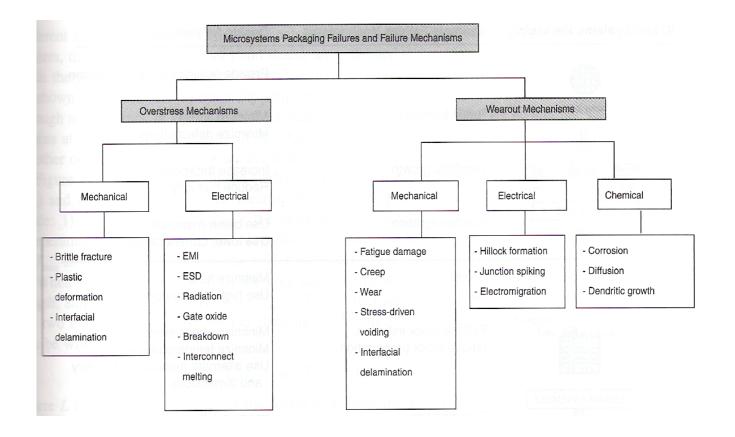

# **Packaging Reliability**

- Testing is required before a new device can be delivered to the market

- Provide the information for the following improvement of packaging design and fabrication

- Use mathematical tools to evaluate data to understand the patterns and identify the sources of failure

| and Systems Packaging      | Example Failure Mechanisms                          | Design for Reliability                                                                                            |  |

|----------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

|                            | Corrosion                                           | Provide sealing and encapsulation                                                                                 |  |

| Wafer & IC                 | Brittle fracture                                    | Minimize stress<br>Minimize defects/flaws                                                                         |  |

| WB FC TAB                  | Dendritic growth                                    | Increase thickness<br>Reduce humidity                                                                             |  |

|                            | Electromigration                                    | Use better materials<br>Use lower current density                                                                 |  |

|                            | Creep                                               | Minimize load<br>Use high temperature materials                                                                   |  |

| Discrete L.C.R Packaged IC | Fatigue crack initiation, fatigue crack propagation | Minimize stress/strain range<br>Minimize temperature range<br>Use alternate materials, geometry<br>and dimensions |  |

| BOARD ASSEMBLY             | Delamination                                        | Improve adhesion                                                                                                  |  |

| •                          | Interdiffusion, slow trapping                       | Lower temperature                                                                                                 |  |

|                            | Radiation damage                                    | Reduce dosage                                                                                                     |  |

| Battery                    | Stress corrosion                                    | Lower stresses<br>Lower humidity<br>Reduce size of defects<br>Lower temperature                                   |  |

| SYSTEM ASSEMBLY            | Contact wear                                        | Minimize stress                                                                                                   |  |

#### **Accelerated Tests**

- Puts a large amount of samples in harsh environments, such as elevated temperature, elevated pressure, and 100% humidity, to accelerate the corrosion process

- The statistical failure data are gathered and analyzed to predict the lifetime of packages under normal usage environment

- As a result, the long-term reliability of the package can be predicted without going through the true long-term tests

#### **Future Trends**

- Development of mechanical, thermal, and electrical models for packaging designs and fabrication processes

- Wafer-level, chip-scale packaging with low packaging cost and high yield

- Effective testing techniques at the wafer level to reduce the testing costs

- Device integrations by vertical throughinterconnects as an interposer to avoid thermal mismatch problems

#### Part II Process Integration (24%)

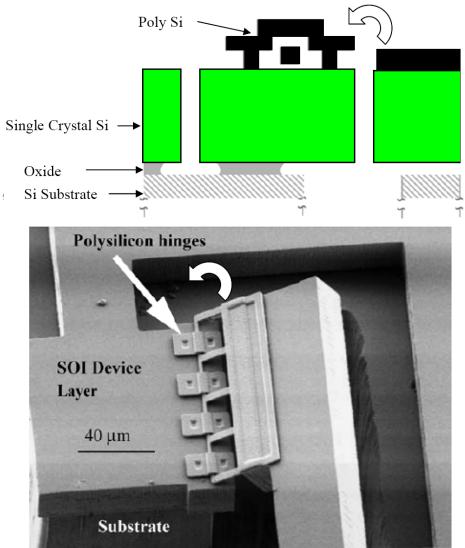

1. Please design a fabrication process for the following structure. (18%)

| Process description | Top/bottom view | Cross-sectional view |

|---------------------|-----------------|----------------------|

| 1                   |                 |                      |

| 2                   |                 |                      |

| 3                   |                 | SOI wafer            |

| 4                   |                 |                      |

| 5                   |                 |                      |

#### 2. Please design a fabrication process for the following structure. (6%)

| Process description | Cross-sectional view |                             |

|---------------------|----------------------|-----------------------------|

| 1                   |                      | Al connect SiO <sub>2</sub> |

| 2                   |                      |                             |

| 3                   |                      | Silicon                     |

| 4                   |                      |                             |

|                     |                      | Pyrex Glass                 |

|                     |                      |                             |